根据台湾经济日报日前的新闻报道,台积电已经在本月初已经开始了 2 纳米工艺的预生产,而英伟达和苹果将有望成为晶圆代工龙头的首批客户,这将给三星等竞争对手带来巨大压力。在回应该报道时,台积电没有评论具体细节,但表示2nm技术的开发进展顺利,目标是在2025年实现量产。

英特尔中国区总裁兼董事长王锐在今年三月的一次活动中表示,公司已完成intel 18A(1.8nm)和intel 20A(2nm) 制造工艺的开发。其中,intel 20A计划于 2024 年上半年投入使用,进展良好的intel 18A制造技术也将提前到2024年下半年进入大批量制造(HVM)。

与此同时,晶圆代工老二三星在今日举办的代工论坛论坛上也重申了公司将在2025年实现2nm生产。再加上日本新成立的 Rapidus也想在2025年量产2nm。一场在2025年将进入白热化的战争已经全面打响。

三星密谋已久

这不是三星首次披露其2nm的计划,其实针对这个被广泛看好的“大节点”,这家韩国巨头密谋已久,他们在这次代工论坛上也带来了更多的消息。

据semiwiki报道,与英特尔一样,三星自己的芯片也是自己的代工客户,因此他们在2nm上首先生产的是内部产品,而不是外部代工客户。这当然是 IDM 代工厂的优势,可以结合工艺技术开发自己的芯片。三星拥有开发领先内存的额外优势。

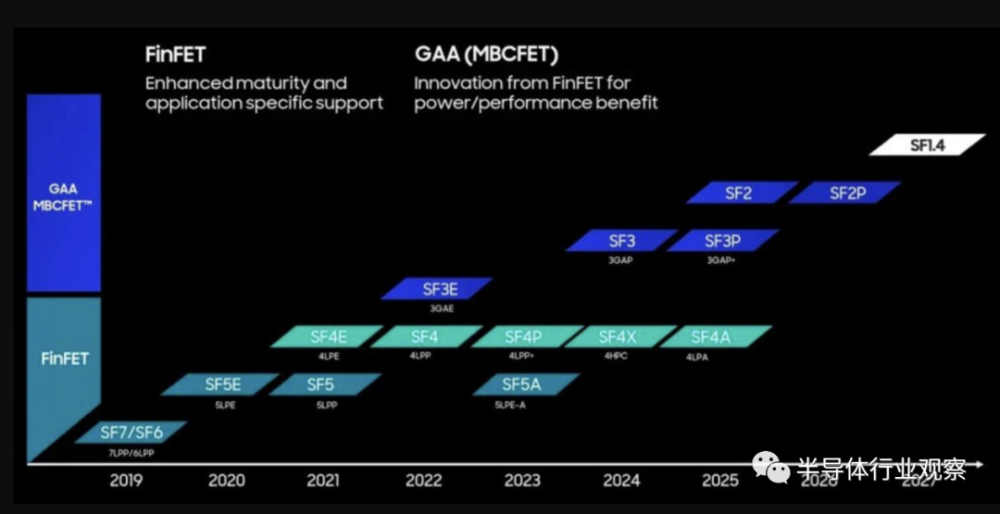

报道指出,三星将于 2025 年开始量产用于移动应用的 2nm 工艺,然后于 2026 年扩展到具有背面供电的 HPC,并于 2027 年扩展到汽车领域。与 3nm 工艺 (SF3) 相比,三星的 2nm (SF2) 工艺已显示出性能提升 12%,功率效率提高提升 25%,面积减少 5%。

按照三星的规划,其GAA MBCFET无疑是2nm工艺的最大竞争优势所在,在上个月的时候,他们就公布了公司在3nm GAA MBCFET技术的最新进展,这将给他们的2nm提供参考。

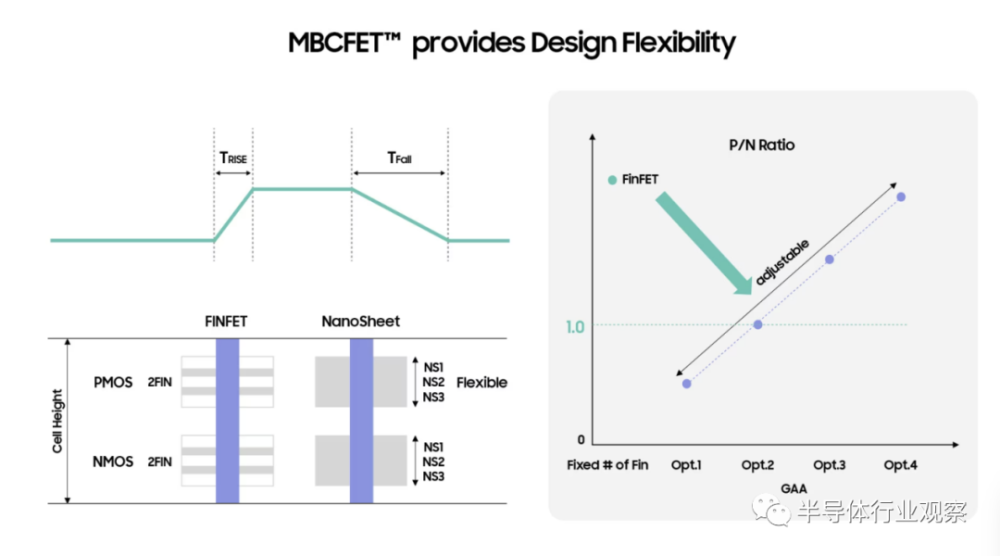

三星表示,与 FinFET 相比,MBCFET 提供了卓越的设计灵活性。晶体管被设计成有不同量的电流流过它们。在使用许多晶体管的半导体中,必须调节电流量,以便在所需的时序和控制逻辑下打开和关闭晶体管,这需要增加或减少沟道的宽度。

而在传统的FinFET结构中,栅极所包裹的鳍片(Fin)的高度是不可调节的,因此为了增加整体沟道宽度,需要水平地增加鳍片的数量。但这种方法只能调节不连续的沟道宽度,因为当栅包围文件的沟道宽度为α时,也只能减小或增大α的倍数。这是一个严重的限制。

另一方面,MBCFET 彼此堆叠在一起,鳍片侧向放置,纳米片的宽度可以调整,以提供比 FinFET 更多的沟道宽度选项,这是一个对整个设计有用的功能,这在模拟 SRAM 中具有显著的优势设计。

”MBCFET 具有这些优势,因为它们的设计允许独立微调晶体管的沟道宽度,以便在 P 型金属氧化物半导体晶体管 (PMOS) 和 N 型金属氧化物半导体晶体管(NMOS)之间找到最佳平衡”,三星强调。